Le risposte su questo thread fino ad ora concordano tutte sul fatto che "dipende". Ho pensato che varrebbe la pena espandere l'area del ciclo menzionata in alcune delle risposte, perché questo è il fattore cruciale qui.

Riguarda l'area del loop formata dal cap e dal chip. È meglio capire cos'è l'area del loop, quindi puoi scegliere il miglior compromesso per qualsiasi situazione. Temo che non esiste una soluzione "fallo in questo modo, sempre".

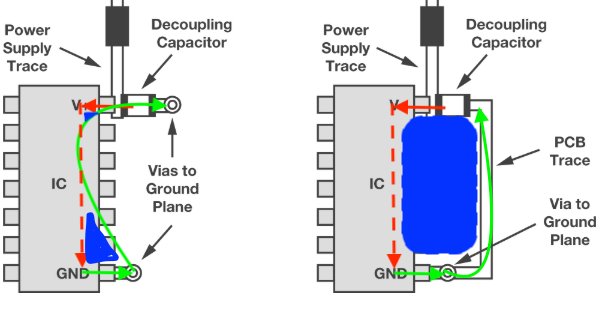

L'area del loop è l'area formata dal percorso della corrente che fluisce nel chip dal cappuccio e dal percorso della corrente che fluisce dal chip al cappuccio. Chiamiamo il percorso in V + e il percorso di ritorno GND.

Per scopi più pratici, fino a una frequenza di 1 GHz, puoi semplicemente guardare l'area del loop dall'alto verso il basso (cioè disegnarla sopra le tue immagini). A frequenze più alte potrebbe essere necessario guardarlo in 3D.

Dove costringi le correnti a fluire in una traccia, il percorso è chiaro: sono le linee delle tracce. Laddove permetti a una corrente di fluire su un piano e l'altra è in tracce, il percorso delle correnti a frequenza più alta sul piano non seguirà il percorso più breve (che potresti aspettarti) - invece cercano di seguire il percorso preso dal corrente limitata alle tracce. La frequenza più bassa o CC sull'aereo fluirà direttamente all'alimentazione e perderà completamente il disaccoppiatore, ma questi non sono interessanti nel contesto del posizionamento del disaccoppiatore.

Ho annotato la tua immagine con l'area loop (vista dall'alto) in ogni caso.

Le linee continue rosse rappresentano i flussi V + dal cappuccio al chip & la linea tratteggiata rossa è il flusso di corrente interno attraverso il chip.

Le linee verdi indicano i flussi GND dal chip al tappo. Nota per l'immagine a sinistra il percorso effettivo preso dalla linea verde da via a via dipenderà dalla frequenza: maggiore è la frequenza, più estrema è la divergenza dal percorso più breve poiché la corrente di ritorno cerca di seguire la corrente diretta.

Le aree blu sono l'area del loop.Puoi vedere qual è il migliore: è quello con meno blu.

Nota che ho ritagliato il testo corretto / errato - dipende interamente dall'applicazione se questo è vero o meno - per alcune applicazioni la soluzione a destra potrebbe essere abbastanza buona e potrebbe consentire altri vantaggi di routing.Tuttavia, è improbabile che sia la soluzione migliore.

Spero che questo aiuti.