Tutti i tappi hanno un circuito equivalente basato su chimica, costruzione e geometria con un minimo di componenti ESR, C, Rleak, ESL mostrati di seguito. Alcuni hanno equiv ccts ancora più complessi. questo è il motivo per cui la sostituzione del cappuccio deve considerare l'applicazione, lo schema, le note di progettazione e il layout per garantire l'assenza di errori nelle scelte.

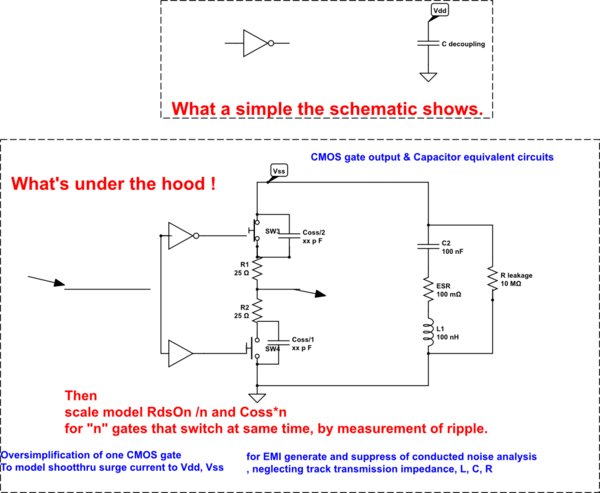

Questa è la realtà dell'elettronica quando i tempi di salita ad alta velocità di commutazione di scarico della capacità di commutazione CMOS devono essere soppressi per migliorare i margini del segnale mediante un adeguato disaccoppiamento di alimentazione e terra.

Questo è anche il motivo per cui alcune persone usano ECL e CML a causa della mancanza di picchi di corrente dalla logica differenziale in modalità corrente quando operano a velocità logiche estreme e necessitano di un'elevata immunità ai disturbi.

Gli MLCC sono tipicamente 2x1 LxW come 1206, 603 402 e quindi hanno una certa induttanza basata su questa dimensione. Ma generalmente hanno una costante di tempo molto bassa rispetto agli elettrolitici quando si utilizza il valore ESR * C = T, il che significa che la frequenza superiore vicino a 1 / T può essere molto più alta per il disaccoppiamento ESR.

- l'uso speciale di MLCC ESL basso LxW = 1x2 esattamente l'opposto per ridurre l'induttanza e quindi aumentare l'SRF, \ $ f = \ frac {1} {2 \ pi \ sqrt { LC}} \ $ realizzato da società come Murata e TDK.

Ora, quando metti molti tappi 2x1 in parallelo in modo tale che LxW diventi largo n, ottieni la stessa cosa riducendo a L / ne aumentando SRF di \ $ \ sqrt n \ $ riducendo l'ESR di n in modo tale che il risultato sia molto migliore di un grande MLCC dello stesso valore uF. Un ESR troppo basso può anche aumentare la Q dei picchi SRF, quando vengono utilizzati più ESR C ultra bassi, quindi leggi i dettagli di Murata TDK su questo se non hai ancora capito.

Ciò è significativo quando è necessario sopprimere i picchi di corrente dalla logica CMOS con tempi di salita > = 1ns che hanno una capacità di Coss di uscita e da 25 a 50 Ω RdsOn per 74ALVCxx o ARM uC o a 50 Ω per 74ALCxx CMOS. Il Coss aumenta con RdsOn ridotto nei MOSFET ma si riduce anche con le dimensioni litografiche. Se immaginate un divisore di capacità con una tensione commutata Vss, non solo il rapporto ESR / RdsOn è importante, ma anche il Coss / C (f) netto per il disaccoppiamento per molti decenni di f.

L'altro fattore è rappresentato dai cappucci distribuiti in modo che l'induttanza della traccia non provochi un SRF inferiore a quello richiesto e la posizione più vicina del cappuccio di disaccoppiamento alla sorgente riduce il rumore di picco Vdd E Vss. Il risultato è spesso ondulazione non solo a causa di metodi di sonda dell'oscilloscopio scadenti, ma anche della funzione di trasferimento dei picchi con frequenze di risonanza e riduzione del rapporto C e riduzione del rapporto ESR. (Entrambi sono divisori di tensione quando f < SRF))

simula questo circuito. Schema creato utilizzando CircuitLab

Il tempo di salita varia in base alla famiglia CMOS e i picchi di corrente dipendono dal numero di interruttori sincroni all'interno dell'IC o del gruppo di CI